# Chapter 20

# Universal Serial Communication Interface, SPI Mode

The universal serial communication interface (USCI) supports multiple serial communication modes with one hardware module. This chapter discusses the operation of the synchronous peripheral interface or SPI mode.

| Topic | 5                           | Page   |

|-------|-----------------------------|--------|

| 20.1  | USCI Overview               | . 20-2 |

| 20.2  | USCI Introduction: SPI Mode | . 20-3 |

| 20.3  | USCI Operation: SPI Mode    | . 20-5 |

| 20.4  | USCI Registers: SPI Mode    | 20-14  |

## 20.1 USCI Overview

The universal serial communication interface (USCI) modules support multiple serial communication modes. Different USCI modules support different modes. Each different USCI module is named with a different letter. For example, USCI\_A is different from USCI\_B, etc. If more than one identical USCI module is implemented on one device, those modules are named with incrementing numbers. For example, if one device has two USCI\_A modules, they are named USCI\_A0 and USCI\_A1. See the device-specific data sheet to determine which USCI modules, if any, are implemented on which devices.

The USCI\_Ax modules support:

- UART mode

- Pulse shaping for IrDA communications

- Automatic baud rate detection for LIN communications

- SPI mode

The USCI\_Bx modules support:

- □ I<sup>2</sup>C mode

- SPI mode

## 20.2 USCI Introduction: SPI Mode

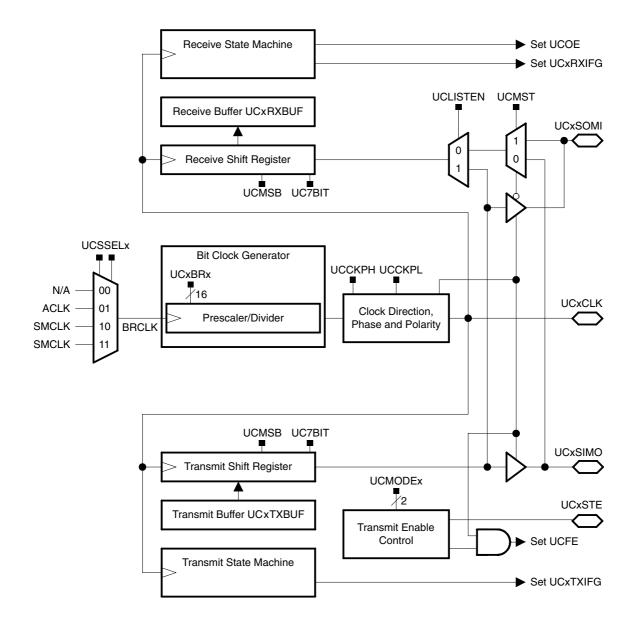

In synchronous mode, the USCI connects the MSP430 to an external system via three or four pins: UCxSIMO, UCxSOMI, UCxCLK, and UCxSTE. SPI mode is selected when the UCSYNC bit is set and SPI mode (3-pin or 4-pin) is selected with the UCMODEx bits.

SPI mode features include:

- 7- or 8-bit data length

- LSB-first or MSB-first data transmit and receive

- □ 3-pin and 4-pin SPI operation

- Master or slave modes

- Independent transmit and receive shift registers

- Separate transmit and receive buffer registers

- Continuous transmit and receive operation

- Selectable clock polarity and phase control

- Programmable clock frequency in master mode

- Independent interrupt capability for receive and transmit

- □ Slave operation in LPM4

Figure 20–1 shows the USCI when configured for SPI mode.

# 20.3 USCI Operation: SPI Mode

In SPI mode, serial data is transmitted and received by multiple devices using a shared clock provided by the master. An additional pin, UCxSTE, is provided to enable a device to receive and transmit data and is controlled by the master.

Three or four signals are used for SPI data exchange:

|        | Slave in, master out<br>Master mode: UCxSIMO is the data output line.<br>Slave mode: UCxSIMO is the data input line.                                    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Slave out, master in<br>Master mode: UCxSOMI is the data input line.<br>Slave mode: UCxSOMI is the data output line.                                    |

|        | USCI SPI clock<br>Master mode: UCxCLK is an output.<br>Slave mode: UCxCLK is an input.                                                                  |

| UCxSTE | Slave transmit enable. Used in 4-pin mode to allow multiple masters on a single bus. Not used in 3-pin mode. Table 20–1 describes the UCxSTE operation. |

### Table 20–1. UCxSTE Operation

| UCMODEx | UCxSTE Active State | UCxSTE | Slave    | Master   |

|---------|---------------------|--------|----------|----------|

|         |                     | 0      | inactive | active   |

| 01      | high                | 1      | active   | inactive |

| 10      | laur                | 0      | active   | inactive |

| 10      | low                 | 1      | inactive | active   |

#### 20.3.1 USCI Initialization and Reset

The USCI is reset by a PUC or by the UCSWRST bit. After a PUC, the UCSWRST bit is automatically set, keeping the USCI in a reset condition. When set, the UCSWRST bit resets the UCxRXIE, UCxTXIE, UCxRXIFG, UCOE, and UCFE bits and sets the UCxTXIFG flag. Clearing UCSWRST releases the USCI for operation.

#### Note: Initializing or Re-Configuring the USCI Module

The recommended USCI initialization/re-configuration process is:

- 1) Set UCSWRST (BIS.B #UCSWRST, &UCxCTL1)

- 2) Initialize all USCI registers with UCSWRST=1 (including UCxCTL1)

- 3) Configure ports.

- 4) Clear UCSWRST via software (BIC.B #UCSWRST, &UCxCTL1)

- 5) Enable interrupts (optional) via UCxRXIE and/or UCxTXIE

#### 20.3.2 Character Format

The USCI module in SPI mode supports 7- and 8-bit character lengths selected by the UC7BIT bit. In 7-bit data mode, UCxRXBUF is LSB justified and the MSB is always reset. The UCMSB bit controls the direction of the transfer and selects LSB or MSB first.

#### Note: Default Character Format

The default SPI character transmission is LSB first. For communication with other SPI interfaces it MSB-first mode may be required.

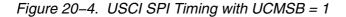

#### Note: Character Format for Figures

Figures throughout this chapter use MSB first format.

#### 20.3.3 Master Mode

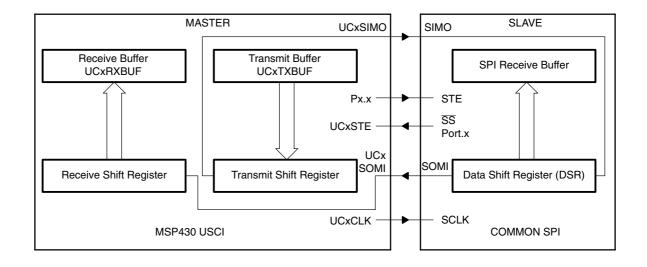

Figure 20–2. USCI Master and External Slave

Figure 20–2 shows the USCI as a master in both 3-pin and 4-pin configurations. The USCI initiates data transfer when data is moved to the transmit data buffer UCxTXBUF. The UCxTXBUF data is moved to the TX shift register when the TX shift register is empty, initiating data transfer on UCxSIMO starting with either the most-significant or least-significant bit depending on the UCMSB setting. Data on UCxSOMI is shifted into the receive shift register on the opposite clock edge. When the character is received, the receive data is moved from the RX shift register to the received data buffer UCxRXBUF and the receive interrupt flag, UCxRXIFG, is set, indicating the RX/TX operation is complete.

A set transmit interrupt flag, UCxTXIFG, indicates that data has moved from UCxTXBUF to the TX shift register and UCxTXBUF is ready for new data. It does not indicate RX/TX completion.

To receive data into the USCI in master mode, data must be written to UCxTXBUF because receive and transmit operations operate concurrently.

#### Four-Pin SPI Master Mode

In 4-pin master mode, UCxSTE is used to prevent conflicts with another master and controls the master as described in Table 20–1. When UCxSTE is in the master-inactive state:

- UCxSIMO and UCxCLK are set to inputs and no longer drive the bus

- ☐ The error bit UCFE is set indicating a communication integrity violation to be handled by the user.

- The internal state machines are reset and the shift operation is aborted.

If data is written into UCxTXBUF while the master is held inactive by UCxSTE, it will be transmit as soon as UCxSTE transitions to the master-active state. If an active transfer is aborted by UCxSTE transitioning to the master-inactive state, the data must be re-written into UCxTXBUF to be transferred when UCxSTE transitions back to the master-active state. The UCxSTE input signal is not used in 3-pin master mode.

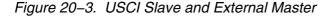

#### 20.3.4 Slave Mode

Figure 20–3 shows the USCI as a slave in both 3-pin and 4-pin configurations. UCxCLK is used as the input for the SPI clock and must be supplied by the external master. The data-transfer rate is determined by this clock and not by the internal bit clock generator. Data written to UCxTXBUF and moved to the TX shift register before the start of UCxCLK is transmitted on UCxSOMI. Data on UCxSIMO is shifted into the receive shift register on the opposite edge of UCxCLK and moved to UCxRXBUF when the set number of bits are received. When data is moved from the RX shift register to UCxRXBUF, the UCxRXIFG interrupt flag is set, indicating that data has been received. The overrun error bit, UCOE, is set when the previously received data is not read from UCxRXBUF before new data is moved to UCxRXBUF.

## Four-Pin SPI Slave Mode

In 4-pin slave mode, UCxSTE is used by the slave to enable the transmit and receive operations and is provided by the SPI master. When UCxSTE is in the slave-active state, the slave operates normally. When UCxSTE is in the slave-inactive state:

- Any receive operation in progress on UCxSIMO is halted

- UCxSOMI is set to the input direction

- □ The shift operation is halted until the UCxSTE line transitions into the slave transmit active state.

The UCxSTE input signal is not used in 3-pin slave mode.

### 20.3.5 SPI Enable

When the USCI module is enabled by clearing the UCSWRST bit it is ready to receive and transmit. In master mode the bit clock generator is ready, but is not clocked nor producing any clocks. In slave mode the bit clock generator is disabled and the clock is provided by the master.

A transmit or receive operation is indicated by UCBUSY = 1.

A PUC or set UCSWRST bit disables the USCI immediately and any active transfer is terminated.

#### **Transmit Enable**

In master mode, writing to UCxTXBUF activates the bit clock generator and the data will begin to transmit.

In slave mode, transmission begins when a master provides a clock and, in 4-pin mode, when the UCxSTE is in the slave-active state.

#### **Receive Enable**

The SPI receives data when a transmission is active. Receive and transmit operations operate concurrently.

### 20.3.6 Serial Clock Control

UCxCLK is provided by the master on the SPI bus. When UCMST = 1, the bit clock is provided by the USCI bit clock generator on the UCxCLK pin. The clock used to generate the bit clock is selected with the UCSSELx bits. When UCMST = 0, the USCI clock is provided on the UCxCLK pin by the master, the bit clock generator is not used, and the UCSSELx bits are don't care. The SPI receiver and transmitter operate in parallel and use the same clock source for data transfer.

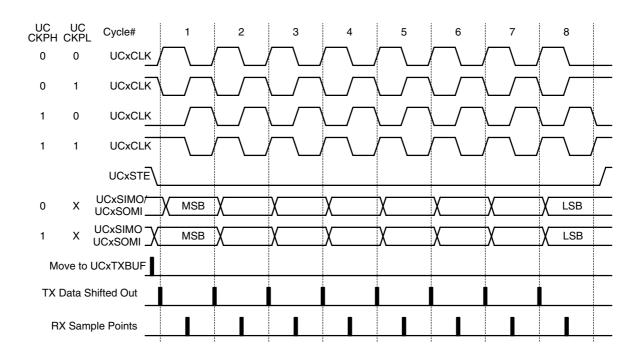

The 16-bit value of UCBRx in the bit rate control registers UCxxBR1 and UCxxBR0 is the division factor of the USCI clock source, BRCLK. The maximum bit clock that can be generated in master mode is BRCLK. Modulation is not used in SPI mode and UCAxMCTL should be cleared when using SPI mode for USCI\_A. The UCAxCLK/UCBxCLK frequency is given by:

$$f_{BitClock} = \frac{f_{BRCLK}}{UCBRx}$$

#### **Serial Clock Polarity and Phase**

The polarity and phase of UCxCLK are independently configured via the UCCKPL and UCCKPH control bits of the USCI. Timing for each case is shown in Figure 20–4.

### 20.3.7 Using the SPI Mode with Low Power Modes

The USCI module provides automatic clock activation for SMCLK for use with low-power modes. When SMCLK is the USCI clock source, and is inactive because the device is in a low-power mode, the USCI module automatically activates it when needed, regardless of the control-bit settings for the clock source. The clock remains active until the USCI module returns to its idle condition. After the USCI module returns to the idle condition, control of the clock source reverts to the settings of its control bits. Automatic clock activation is not provided for ACLK.

When the USCI module activates an inactive clock source, the clock source becomes active for the whole device and any peripheral configured to use the clock source may be affected. For example, a timer using SMCLK will increment while the USCI module forces SMCLK active.

In SPI slave mode no internal clock source is required because the clock is provided by the external master. It is possible to operate the USCI in SPI slave mode while the device is in LPM4 and all clock sources are disabled. The receive or transmit interrupt can wake up the CPU from any low power mode.

#### 20.3.8 SPI Interrupts

The USCI has one interrupt vector for transmission and one interrupt vector for reception.

#### **SPI Transmit Interrupt Operation**

The UCxTXIFG interrupt flag is set by the transmitter to indicate that UCxTXBUF is ready to accept another character. An interrupt request is generated if UCxTXIE and GIE are also set. UCxTXIFG is automatically reset if a character is written to UCxTXBUF. UCxTXIFG is set after a PUC or when UCSWRST = 1. UCxTXIE is reset after a PUC or when UCSWRST = 1.

#### Note: Writing to UCxTXBUF in SPI Mode

Data written to UCxTXBUF when UCxTXIFG = 0 may result in erroneous data transmission.

#### **SPI Receive Interrupt Operation**

The UCxRXIFG interrupt flag is set each time a character is received and loaded into UCxRXBUF. An interrupt request is generated if UCxRXIE and GIE are also set. UCxRXIFG and UCxRXIE are reset by a system reset PUC signal or when UCSWRST = 1. UCxRXIFG is automatically reset when UCxRXBUF is read.

#### **USCI Interrupt Usage**

USCI\_Ax and USCI\_Bx share the same interrupt vectors. The receive interrupt flags UCAxRXIFG and UCBxRXIFG are routed to one interrupt vector, the transmit interrupt flags UCAxTXIFG and UCBxTXIFG share another interrupt vector.

#### Shared Interrupt Vectors Software Example

The following software example shows an extract of an interrupt service routine to handle data receive interrupts from USCI\_A0 in either UART or SPI mode and USCI\_B0 in SPI mode.

```

USCIA0_RX_USCIB0_RX_ISR

BIT.B #UCA0RXIFG, &IFG2 ; USCI_A0 Receive Interrupt?

JNZ USCIA0_RX_ISR

USCIB0_RX_ISR?

; Read UCB0RXBUF (clears UCB0RXIFG)

...

RETI

USCIA0_RX_ISR

; Read UCA0RXBUF (clears UCA0RXIFG)

...

RETI

```

The following software example shows an extract of an interrupt service routine to handle data transmit interrupts from USCI\_A0 in either UART or SPI mode and USCI\_B0 in SPI mode.

```

USCIA0_TX_USCIB0_TX_ISR

BIT.B #UCA0TXIFG, &IFG2 ; USCI_A0 Transmit Interrupt?

JNZ USCIA0_TX_ISR

USCIB0_TX_ISR

; Write UCB0TXBUF (clears UCB0TXIFG)

...

RETI

USCIA0_TX_ISR

; Write UCA0TXBUF (clears UCA0TXIFG)

...

RETI

```

## 20.4 USCI Registers: SPI Mode

The USCI registers applicable in SPI mode for USCI\_A0 and USCI\_B0 are listed in Table 20–2. Registers applicable in SPI mode for USCI\_A1 and USCI\_B1 are listed in Table 20–3.

Table 20–2. USCI\_A0 and USCI\_B0 Control and Status Registers

| Register                             | Short Form | Register Type | Address | Initial State  |

|--------------------------------------|------------|---------------|---------|----------------|

| USCI_A0 control register 0           | UCA0CTL0   | Read/write    | 060h    | Reset with PUC |

| USCI_A0 control register 1           | UCA0CTL1   | Read/write    | 061h    | 001h with PUC  |

| USCI_A0 Baud rate control register 0 | UCA0BR0    | Read/write    | 062h    | Reset with PUC |

| USCI_A0 Baud rate control register 1 | UCA0BR1    | Read/write    | 063h    | Reset with PUC |

| USCI_A0 modulation control register  | UCA0MCTL   | Read/write    | 064h    | Reset with PUC |

| USCI_A0 status register              | UCA0STAT   | Read/write    | 065h    | Reset with PUC |

| USCI_A0 Receive buffer register      | UCA0RXBUF  | Read          | 066h    | Reset with PUC |

| USCI_A0 Transmit buffer register     | UCA0TXBUF  | Read/write    | 067h    | Reset with PUC |

| USCI_B0 control register 0           | UCB0CTL0   | Read/write    | 068h    | 001h with PUC  |

| USCI_B0 control register 1           | UCB0CTL1   | Read/write    | 069h    | 001h with PUC  |

| USCI_B0 Bit rate control register 0  | UCB0BR0    | Read/write    | 06Ah    | Reset with PUC |

| USCI_B0 Bit rate control register 1  | UCB0BR1    | Read/write    | 06Bh    | Reset with PUC |

| USCI_B0 status register              | UCB0STAT   | Read/write    | 06Dh    | Reset with PUC |

| USCI_B0 Receive buffer register      | UCB0RXBUF  | Read          | 06Eh    | Reset with PUC |

| USCI_B0 Transmit buffer register     | UCB0TXBUF  | Read/write    | 06Fh    | Reset with PUC |

| SFR interrupt enable register 2      | IE2        | Read/write    | 001h    | Reset with PUC |

| SFR interrupt flag register 2        | IFG2       | Read/write    | 003h    | 00Ah with PUC  |

#### Note: Modifying SFR bits

To avoid modifying control bits of other modules, it is recommended to set or clear the IEx and IFGx bits using BIS.B or BIC.B instructions, rather than MOV.B or CLR.B instructions.

| Register                             | Short Form | Register Type | Address | Initial State  |

|--------------------------------------|------------|---------------|---------|----------------|

| USCI_A1 control register 0           | UCA1CTL0   | Read/write    | 0D0h    | Reset with PUC |

| USCI_A1 control register 1           | UCA1CTL1   | Read/write    | 0D1h    | 001h with PUC  |

| USCI_A1 Baud rate control register 0 | UCA1BR0    | Read/write    | 0D2h    | Reset with PUC |

| USCI_A1 Baud rate control register 1 | UCA1BR1    | Read/write    | 0D3h    | Reset with PUC |

| USCI_A1 modulation control register  | UCA1MCTL   | Read/write    | 0D4h    | Reset with PUC |

| USCI_A1 status register              | UCA1STAT   | Read/write    | 0D5h    | Reset with PUC |

| USCI_A1 Receive buffer register      | UCA1RXBUF  | Read          | 0D6h    | Reset with PUC |

| USCI_A1 Transmit buffer register     | UCA1TXBUF  | Read/write    | 0D7h    | Reset with PUC |

| USCI_B1 control register 0           | UCB1CTL0   | Read/write    | 0D8h    | 001h with PUC  |

| USCI_B1 control register 1           | UCB1CTL1   | Read/write    | 0D9h    | 001h with PUC  |

| USCI_B1 Bit rate control register 0  | UCB1BR0    | Read/write    | 0DAh    | Reset with PUC |

| USCI_B1 Bit rate control register 1  | UCB1BR1    | Read/write    | 0DBh    | Reset with PUC |

| USCI_B1 status register              | UCB1STAT   | Read/write    | 0DDh    | Reset with PUC |

| USCI_B1 Receive buffer register      | UCB1RXBUF  | Read          | 0DEh    | Reset with PUC |

| USCI_B1 Transmit buffer register     | UCB1TXBUF  | Read/write    | 0DFh    | Reset with PUC |

| USCI_A1/B1 interrupt enable register | UC1IE      | Read/write    | 006h    | Reset with PUC |

| USCI_A1/B1 interrupt flag register   | UC1IFG     | Read/write    | 007h    | 00Ah with PUC  |

# Table 20–3. USCI\_A1 and USCI\_B1 Control and Status Registers

## UCAxCTL0, USCI\_Ax Control Register 0 UCBxCTL0, USCI\_Bx Control Register 0

| -                                                                                                                                                                                                               | 7       | 6                 | 5                                                                                                                     | 4                                      | 3              | 2             | 1          | 0          |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------|---------------|------------|------------|--|

|                                                                                                                                                                                                                 | ИССКРН  | UCCKPL            | UCMSB                                                                                                                 | UC7BIT                                 | UCMST          | UCMC          | DDEx       | UCSYNC=1   |  |

|                                                                                                                                                                                                                 | rw-0    | rw-0              | rw-0                                                                                                                  | rw-0                                   | rw-0           | rw-0          | rw-0       | rw-0       |  |

| <ul> <li>UCCKPH Bit 7 Clock phase select.</li> <li>0 Data is changed on the first UCLK edge and ca<br/>following edge.</li> <li>1 Data is captured on the first UCLK edge and ch<br/>following edge.</li> </ul> |         |                   |                                                                                                                       |                                        |                |               |            |            |  |

| ι                                                                                                                                                                                                               | JCCKPL  | C                 | Clock polarity select.<br>0 The inactive state is low.<br>1 The inactive state is high.                               |                                        |                |               |            |            |  |

| ι                                                                                                                                                                                                               | JCMSB   | r<br>C            | MSB first select. Controls the direction of the receive and transmit shift<br>register.<br>0 LSB first<br>1 MSB first |                                        |                |               |            |            |  |

| ι                                                                                                                                                                                                               | JC7BIT  | Bit 4 C           |                                                                                                                       | a                                      | 7-bit or 8-bit | character ler | ngth.      |            |  |

| ι                                                                                                                                                                                                               | JCMST   | C                 | Master mode<br>) Slave m<br>I Master r                                                                                | ode                                    |                |               |            |            |  |

| l                                                                                                                                                                                                               | JCMODEx | 2-1 L<br>C<br>1   |                                                                                                                       | 임<br>임 with UCxS<br>임 with UCxS        | TE active hi   | -             | abled when | UCxSTE = 1 |  |

| ι                                                                                                                                                                                                               | JCSYNC  | Bit 0 S<br>C<br>1 |                                                                                                                       | mode enable<br>onous mode<br>nous Mode |                |               |            |            |  |

## UCAxCTL1, USCI\_Ax Control Register 1 UCBxCTL1, USCI\_Bx Control Register 1

| -                                                                  | 7       | 6           |                | 5                                                                                                                | 4    | 3    | 2    | 1    | 0        |

|--------------------------------------------------------------------|---------|-------------|----------------|------------------------------------------------------------------------------------------------------------------|------|------|------|------|----------|

|                                                                    | UCS     | SELx        |                | Unused                                                                                                           |      |      |      |      | UCSWRST  |

|                                                                    | rw-0    | rw-0        |                | rw-0†<br>r0‡                                                                                                     | rw-0 | rw-0 | rw-0 | rw-0 | rw-1     |

| <sup>†</sup> UCAxCTL1 (USCI_Ax)<br><sup>‡</sup> UCBxCTL1 (USCI_Bx) |         |             |                |                                                                                                                  |      |      |      |      |          |

| ι                                                                  | JCSSELx | Bits<br>7-6 |                | 01 ACLK<br>10 SMCLK                                                                                              |      |      |      |      | clock in |

| ι                                                                  | Jnused  | Bits<br>5-1 | Unu            | Unused in synchronous mode (UCSYNC=1).                                                                           |      |      |      |      |          |

| ι                                                                  | JCSWRST | Bit 0       | Soft<br>0<br>1 | oftware reset enable<br>Disabled. USCI reset released for operation.<br>Enabled. USCI logic held in reset state. |      |      |      |      |          |

## UCAxBR0, USCI\_Ax Bit Rate Control Register 0 UCBxBR0, USCI\_Bx Bit Rate Control Register 0

# UCAxSTAT, USCI\_Ax Status Register UCBxSTAT, USCI\_Bx Status Register

|   | 7                                                                                                                                                    | 6           | 5                                                                                                                                                                            | 4                                             | 3                                            | 2                           | 1             | 0       |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|-----------------------------|---------------|---------|

|   | UCLISTEN                                                                                                                                             | UCFE        | UCOE                                                                                                                                                                         | Unused                                        | Unused                                       | Unused                      | Unused        | UCBUSY  |

| - | rw-0                                                                                                                                                 | rw-0        | rw-0                                                                                                                                                                         | rw-0†<br>r0‡                                  | rw-0                                         | rw-0                        | rw-0          | r-0     |

|   | <sup>†</sup> UCAxSTAT (USCI_Ax)<br><sup>‡</sup> UCBxSTAT (USCI_Bx)                                                                                   |             |                                                                                                                                                                              |                                               |                                              |                             |               |         |

| ι | UCLISTENBit 7Listen enable. The UCLISTEN bit selects loopback mode.0Disabled1Enabled. The transmitter output is internally fed back to the receiver. |             |                                                                                                                                                                              |                                               |                                              |                             |               |         |

| ι | JCFE                                                                                                                                                 | Bit 6       | Framing error flag. This bit indicates a bus conflict in 4-wire master mode<br>UCFE is not used in 3-wire master or any slave mode.<br>0 No error<br>1 Bus conflict occurred |                                               |                                              |                             |               |         |

| ι | ICOE                                                                                                                                                 | Bit 5       | Overrun error<br>UCxRXBUF t<br>automatically<br>software. Oth<br>0 No erro<br>1 Overrur                                                                                      | efore the pre<br>when UCxR<br>erwise, it will | evious chara<br>XBUF is read<br>not function | cter was rea<br>d, and must | d. UCOE is    | cleared |

| ι | Inused                                                                                                                                               | Bits<br>4–1 | Unused in sy                                                                                                                                                                 | nchronous m                                   | ode (UCSYN                                   | VC=1).                      |               |         |

| ι | ICBUSY                                                                                                                                               | Bit 0       | USCI busy. T<br>progress.<br>0 USCI in<br>1 USCI tra                                                                                                                         |                                               |                                              | mit or receive              | e operation i | s in    |

# UCAxRXBUF, USCI\_Ax Receive Buffer Register UCBxRXBUF, USCI\_Bx Receive Buffer Register

| 7       | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|----------|---|---|---|---|---|---|--|--|

|         | UCRXBUFx |   |   |   |   |   |   |  |  |

| rrrrrrr |          |   |   |   |   |   |   |  |  |

UCRXBUFx Bits 7-0 The receive-data buffer is user accessible and contains the last received character from the receive shift register. Reading UCxRXBUF resets the receive-error bits, and UCxRXIFG. In 7-bit data mode, UCxRXBUF is LSB justified and the MSB is always reset.

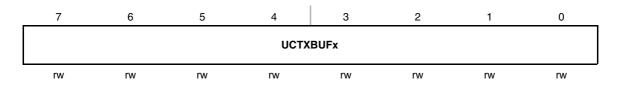

# UCAxTXBUF, USCI\_Ax Transmit Buffer Register UCBxTXBUF, USCI\_Bx Transmit Buffer Register

UCTXBUFx Bits 7-0 Bits The transmit data buffer is user accessible and holds the data waiting to be moved into the transmit shift register and transmitted. Writing to the transmit data buffer clears UCxTXIFG. The MSB of UCxTXBUF is not used for 7-bit data and is reset.

# IE2, Interrupt Enable Register 2

| 7       | 6           | 5                                                                                | 4                                                                 | 3        | 2        | 1        | 0        |

|---------|-------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------|----------|----------|----------|----------|

|         |             |                                                                                  |                                                                   | UCB0TXIE | UCB0RXIE | UCA0TXIE | UCA0RXIE |

|         |             | -                                                                                | -                                                                 | rw-0     | rw-0     | rw-0     | rw-0     |

|         | Bits<br>7-4 | These bits ma                                                                    | These bits may be used by other modules. See device-specific data |          |          |          |          |

| UCB0TXI | E Bit 3     | 0 Interrup                                                                       |                                                                   |          |          |          |          |

| UCB0RXI | E Bit 2     | 0 Interrup                                                                       |                                                                   |          |          |          |          |

| UCA0TXI | E Bit 1     | USCI_A0 transmit interrupt enable<br>0 Interrupt disabled<br>1 Interrupt enabled |                                                                   |          |          |          |          |

| UCAORXI | E Bit 0     | •                                                                                | eive interrupt<br>t disabled<br>t enabled                         | enable   |          |          |          |

# IFG2, Interrupt Flag Register 2

| 7             | 6           | 5                                                                                                                              | 4 | 3             | 2             | 1             | 0             |

|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------|---|---------------|---------------|---------------|---------------|

|               |             |                                                                                                                                |   | UCB0<br>TXIFG | UCB0<br>RXIFG | UCA0<br>TXIFG | UCA0<br>RXIFG |

|               |             |                                                                                                                                |   | rw-1          | rw-0          | rw-1          | rw-0          |

|               | Bits<br>7-4 | These bits may be used by other modules. See device-specific data sheet.                                                       |   |               |               |               |               |

| UCB0<br>TXIFG | Bit 3       | USCI_B0 transmit interrupt flag. UCB0TXIFG is set when UCB0TXBUF is<br>empty.<br>0 No interrupt pending<br>1 Interrupt pending |   |               |               |               |               |

| UCB0<br>RXIFG | Bit 2       |                                                                                                                                |   | icter.        | RXIFG is set  | when UCB      | RXBUF has     |

| UCA0<br>TXIFG | Bit 1       | USCI_A0 transmit interrupt flag. UCA0TXIFG is set when UCA0TXBUF<br>empty.<br>0 No interrupt pending<br>1 Interrupt pending    |   |               |               |               |               |

| UCA0<br>RXIFG | Bit 0       |                                                                                                                                |   | icter.        | RXIFG is set  | when UCA      | )RXBUF has    |

# UC1IE, USCI\_A1/USCI\_B1 Interrupt Enable Register

|   | 7        | 6           | 5      | 4                                         | 3        | 2        | 1        | 0        |

|---|----------|-------------|--------|-------------------------------------------|----------|----------|----------|----------|

|   | Unused   | Unused      | Unused | Unused                                    | UCB1TXIE | UCB1RXIE | UCA1TXIE | UCA1RXIE |

|   | rw–0     | rw–0        | rw–0   | rw–0                                      | rw–0     | rw–0     | rw–0     | rw–0     |

| ι | Inused   | Bits<br>7-4 | Unused |                                           |          |          |          |          |

| ι | JCB1TXIE | Bit 3       |        | smit interrup<br>t disabled<br>t enabled  | t enable |          |          |          |

| ι | JCB1RXIE | Bit 2       | •      | eive interrupt<br>t disabled<br>t enabled | enable   |          |          |          |

| ι | JCA1TXIE | Bit 1       |        | smit interrup<br>t disabled<br>t enabled  | t enable |          |          |          |

| ι | JCA1RXIE | Bit 0       |        | eive interrupt<br>t disabled<br>t enabled | enable   |          |          |          |

# UC1IFG, USCI\_A1/USCI\_B1 Interrupt Flag Register

|               | 7      | 7 6         |                                                                                                                                                                                 | 5      | 4      | 3             | 2             | 1             | 0             |

|---------------|--------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|---------------|---------------|---------------|---------------|

|               | Unused | Unused      |                                                                                                                                                                                 | Unused | Unused | UCB1<br>TXIFG | UCB1<br>RXIFG | UCA1<br>TXIFG | UCA1<br>RXIFG |

|               | rw–0   | rw–0        |                                                                                                                                                                                 | rw–0   | rw–0   | rw–1          | rw–0          | rw–1          | rw–0          |

| Unused        |        | Bits<br>7-4 | Unused                                                                                                                                                                          |        |        |               |               |               |               |

| UCB1<br>TXIFG |        | Bit 3       | USCI_B1 transmit interrupt flag. UCB1TXIFG is set when UCB1TXBUF is<br>empty.<br>0 No interrupt pending<br>1 Interrupt pending                                                  |        |        |               |               |               |               |

| UCB1<br>RXIFG |        | Bit 2       | <ul> <li>USCI_B1 receive interrupt flag. UCB1RXIFG is set when UCB1RXBUF has received a complete character.</li> <li>No interrupt pending</li> <li>Interrupt pending</li> </ul> |        |        |               |               |               |               |

| UCA1<br>TXIFG |        | Bit 1       | USCI_A1 transmit interrupt flag. UCA1TXIFG is set when UCA1TXBUF<br>empty.<br>0 No interrupt pending<br>1 Interrupt pending                                                     |        |        |               |               |               |               |

| UCA1<br>RXIFG |        | Bit 0       | <ul> <li>USCI_A1 receive interrupt flag. UCA1RXIFG is set when UCA1RXBUF has received a complete character.</li> <li>No interrupt pending</li> <li>Interrupt pending</li> </ul> |        |        |               |               |               |               |